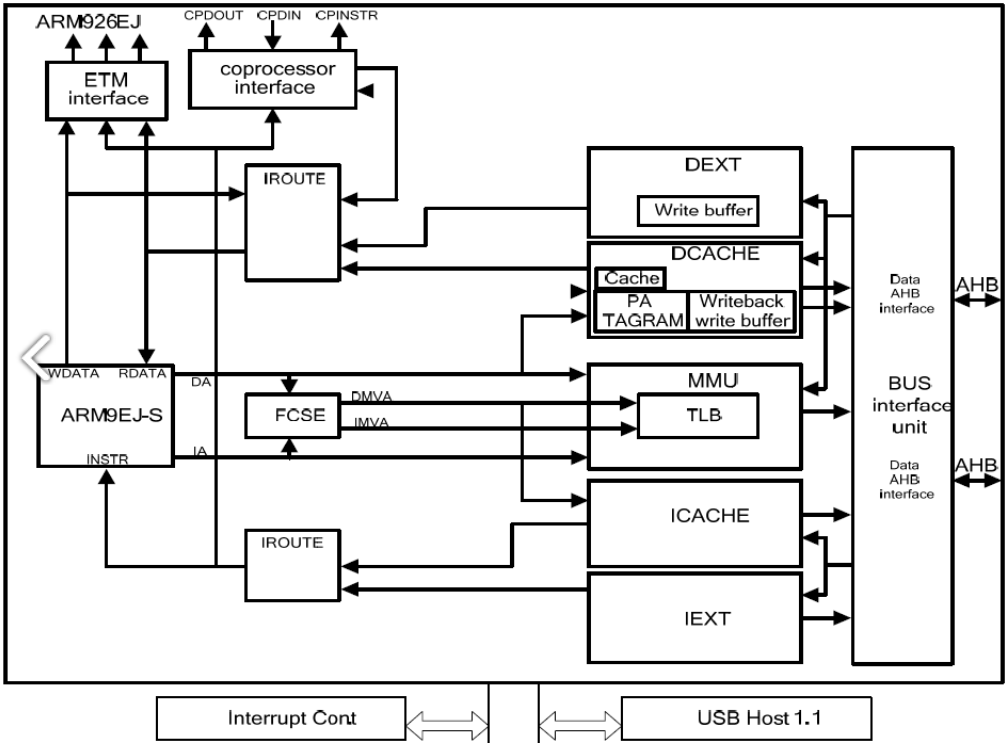

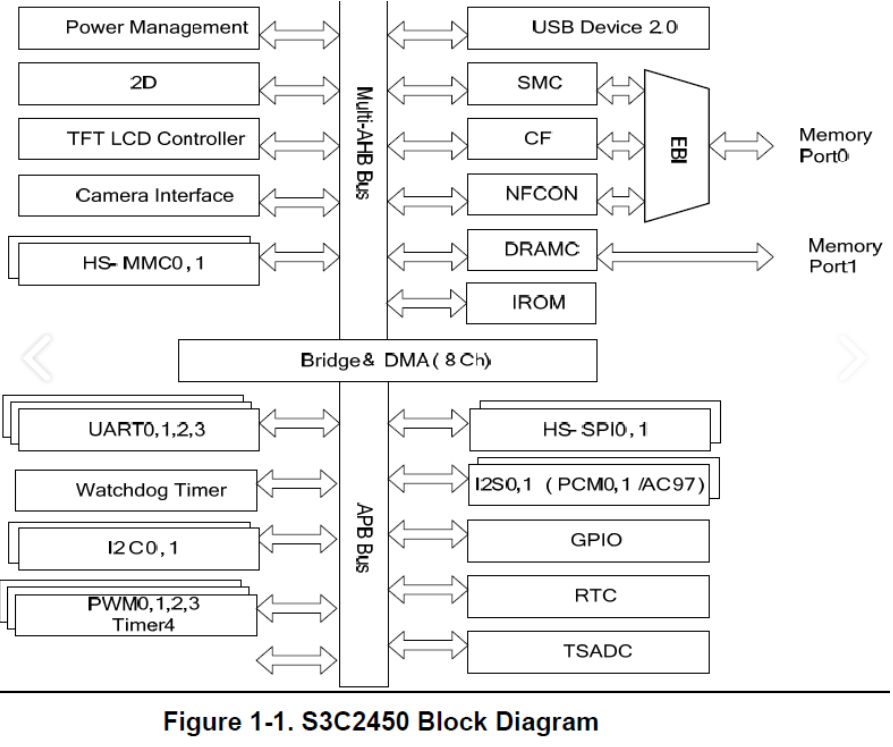

○ ARM core 구조에 관한 대부분의 설명과 사진은 s3c2450 user manual에 있다.

◎ 블록 다이어그램 다시 보기

● AMBA 버스

▷ AMBA(Advanced Microcontroller Bus Architecture)

- ARM에서 개발하여 오픈 한 표준 시스템 버스 설계 구격

- SoC를 구성하는 기능 블록들 간의 연결 및 관리 방법을 제공

▷ 표준 AMBA 버스의 장점

- SoC 설계자 간의 의사소통 용이

:: 설계자 간의 idea공유로 SoC 설계 시간 단축

- IP(Intellenctual Property)의 재사용이 용이

:: 외부의 표준 IP 도입으로 SoC 설계 시간 단축

▷ AHB (Advanced High-performance Bus)

- High performance

▷ APB(Advanced Peripheral Bus)

- Peripheral bus

▷ AXI(Advanced eXtensible Interface)

- AMBA 버스 Spec 3.0

- High performance, High frequency and Low Power)

○ AHB 버스

- high performance 지원

- pipelined operation 지원

- multiple bus master 지원

- Burst transfer 지원(RAM, DMA 등 우르르 보냄)

- Single clock edge를 사용하여 동작 (Rising edge) (*DDR 이란? double data의 약자. 클럭의 rising, falling에 둘 다 동작)

- AHB Master와 Slave, Arbiter : 한 번에 하나의 마스터가 읽기 또는 쓰기 동작을 Arbiter에게 요청, 요청에 따라 Slave가 동작 수행. 참고하기 좋은 임베디드 레시피

AMBA - SoC안에서 IP끼리의 Bus 규격

recipes.egloos.com

○ APB 버스

- Low Power (clock속도가 떨어짐.)

★ S3C2450의 이해

● Clock 설정.

▷ 보통, 시스템의 동작은 외부의 낮은 Clock을 PPL을 통해 높은 Clock으로 증가시키고 이를 동작 clock으로 하여 내부 회로를 구동시킨다.

:: clock 알면 좋은 점

1) 명령어 단위로 NOP(system delay)을 줄 때 clock 알면 정확한 시간 줄 수 있다.

2) 성능을 가늠할 수 있다.

- 외부의 낮은 clock -> PLL -> 높은 동작 Clock

▷ Mpll -> Main Clock ::: 다시 ARMCLK(CORE), HCLK(/4), PCLK(/4/2), DDRCLK로 분주된다.

▷ Epll(Extended) -> USB clock, CAM clock, LCD clock, I2C clock, UART clock으로 출력

▷ SOURCE - 크리스탈(X-TAL), 오실레이터(OSC)(사실 이게 크리스탈 포함.)

- 12MHz(BUS 등의 clock으로)

- 32.768kHz (=2^15 * 0.001) (시계로 많이 씀)

=> 400MHz ~ 533 MHz를 만들어 낸다.

-여기서 /4로 AHB로 들어가고, /2를 더한 /4/2가 APB BUS로 들어간다.

▷ Lock Time

- PLL logic을 통해 외부 X-TAL Clock은 안정된 출력 CLock을 공급하게 되는데 최적화된 출력 clock을 공급할 때까지 시간이 필요하다. 이 구간은 불안정한 상태이기 때문에 Lock time을 설정하여 chip이 동작하지 않게 하고 이후 안정화된 클럭에 의해 동작한다.

*Tip!

(* 보통 Clock과 전력 소비(Power Consumption의 비는 1 : 2이다.)

(* core가 빠른 건 낮은 v에서 유리하다. 낮을수록 rising, fall 이 빨라서.)

(* 3.3V-Cmos Level / 5V-TTL Level)

(* 출력으로 나오는 Clock MPll과 Epll의 계산식이 존재하지만, 보통 data sheet에 sample table이 있기 때문에 그걸 참고하면 된다.)

▷ 보통 ARMCLK : HCLK : PCLK : DDECLK = 1 : 4 : 8 : 2 의 분주비를 갖는다.

○ Power 관리

▷ Normal 모드

- CPU core를 비롯한 모든 제어 block이 정상 동작

- 전력 소모를 줄이기 위해 기본장치를 제외한 나머지 장치들에 대한 동작을 s/w적으로 제어할 수 있다.

▷ IDLE 모드

- bus, memory, interrupt 컨트롤러들과 power management block을 제외한 CPUL core stopped

- 외부 인터럽트, EINT, RTC alarm 인터럽트에 의해 벗어날 수 있다.

▷ STOP 모드

- PLL 없이 저주파를 동작으로 CLOCK으로 사용. 전력 소모를 줄인다. / PWRCFG레지스터로 제어

- Deep-Stop : ARM core의 Internal power gating을 사용 / PWRMODE [18] 레지스터로 제어

▷ SLEEP 모드

- 모든 주변장치를 포함하는 코어 전력을 셧다운 하며 재가동(wake-up) 로직을 제외한 SoC 모든 로직에서는 어떤 전력 소모도 일어나지 않는다.

- EINT[15:0], RTC alarm 인터럽트 등에 의해 POWR_OFF 모드에서 깨어난다.

★ 임베디드 소프트웨어 개발

○ APCS (Arm Procedure Call Standard)

Pipe line과 Exception 관계 그리고 ^접미사

실컷 Exception 관련한 얘기를 했습니다. 뒷 처리 얘기도 해야겠죠. 여자친구랑 데이트 하다가 화장실에 가고 싶어지면 화장실에 갔다 와야겠죠. 화장실에 갔다 오려면 가기 전에 무슨 얘기를 하고

recipes.egloos.com

○ Return From Exception Handler

▷ Exception 처리가 완료되면 다음의 절차를 수행하여 복귀.

- LR_<mode> 값을 PC에 복사한다.

- SPSR_<mode>를 CPSR에 복사한다.

(** 주의사항! 위 2가지의 동작이 하나의 명령으로 처리되어야 한다.)

▷ Exception 복귀 명령

- Data Processing 명령에 S 접미사를 사용하여 PC를 destination 레지스터로 사용하는 방법.

(Privilege 모드에서 S 접미사를 사용하면 명령어의 dst 레지스터가 PC 일 경우 CPSR = SPSR 이 된다.

SUBS PC, LR #4 //접미사 S로 CPSR=SPSR- LDM 명령을 사용하고 register list 뒤에 ^옵션 사용

( stack에 되돌아갈 주소 값이 계산되어 들어가 있어야 한다. )

LDM SP!, {PC}^ // ^는 CPSR 복구하라는 의미

○ Exception 과 Pipeline

▷ Exception 종류별로 CPU에서 발생한 Exception을 인식하는 시점의 Pipeline stage가 모두 다르다.

(Pipe line stage : Fetch - Decode - Excute - Memory Access - Write Back )

- 따라서 복원되는 PC 값의 조정이 필요하다.

▷ Exception 복귀 명령

(R14 는 LR(link register) 과 동일하다. 이 LR을 활용하영 어디서 문제가 생겼는지 debug 할 수 있다.)

* 개인적인 학습 목적으로 작성한 글이기에 내용에 잘못된 정보가 있을 수 있습니다.

'임베디드 개발(before) > IoT 임베디드 SW 개발자 양성과정' 카테고리의 다른 글

| [32일차] ARM 프로세서 이해 및 활용 (switch 실습) (0) | 2020.08.25 |

|---|---|

| [31일차] ARM 프로세서 이해 및 활용 (부트코드 작성, 소프트웨어 최적화, LED 실습) (0) | 2020.08.24 |

| [29일차] ARM 프로세서 이해 및 활용 (Cache, MMU) (0) | 2020.08.21 |

| [28일차] ARM 프로세서 이해 및 활용(ARM 프로세서의 명령어) (0) | 2020.08.20 |

| [27일차] ARM 프로세서 이해 및 활용 (Program Status Register (PSR), Exception) (0) | 2020.08.19 |