1. 임베디드 시스템의 구조

-

프로세서의 구조

1) 레지스터(Register) :

○ 프로세서 내부에서 데이터를 일시적으로 보관하는 기억장치.

- Flip-flop와 Latch로 구성되어 있다.

○ 범용 레지스터. (Ground Port Register)

- 프로그램 또는 데이터 처리에 필요한 작업을 수행하기 위해 사용.

○ 제어용 레지스터. (control)

- 프로그램이나 프로세서를 제어. 프로그램 카운터(PC) 등

○ 상태 레지스터. (Program Status Register)

- 프로세서의 상태를 나타낸다.

2) 산술 논리 연산장치(ALU)

- 산술 연산 수행(덧셈 뺄셈 등)

- 논리 연산 수행(AND, OR 등)

- 상태 레지스터 또는 Flag 레지스터에 연산 결과 기록

- carry 발생, overflow 발생 등

3) 제어장치

- 명령을 해석하고 실행

- 명려을 일고 실행하기 위한 내부 데이터 흐름 제어.

-

프로세서 버스 : 시스템의 여러 장치들을 연결하는 경로. (버스란? 신호선의 집합.)

1) 내부 버스

- 프로세서 내부에서 레지스터와 ALU 사이의 신호를 교환, 그 결과를 다시 레지스터에 전달하는 경로

2) 외부 버스

- 프로세서와 외부의 기억장치 사이, 그리고 프로세서와 I/O장치 사이에 존재하는 입출력 버스

○ 데이터 버스

- 데이터를 외부 장치에 전달하거나 외부 장치로부터 읽어오는 경로

○ 어드레스 버스

- 프로세서에서 기어장치나 I/O 장치의 주소 정보 전송 경로.

○ 제어 버스

- 프로세서에서 기억장치나 I/O장치에 입출력 동작을 지시하는 제어신호를 전송하는 경로.

-

파이프라인 : 한 데이터 처리 단계의 출력이 다음 단계의 입력으로 이어지는 형태로 연결된 구조.

1) 명령어 파이프라인

- 같은 CPU 회로 안에서 여러 명령어들이 단계적으로 수행되는 것.

- 동일 시간 수행될 수 있는 명령어 수 증가.

- 각 명령어는 다시 fetch(명령어 가져오는 거)-decoding(명령어 해석)-execute(실행) 등의 세부 주기로 나뉘어 각 파이프라인 단계에 의해 수행된다.

- 기계어와 어셈블리어

1) 기계어

- 2진수(16진수)로 구성된 명령.

- 프로세서가 바로 실행할 수 있는 형태의 명령

2) 니모닉 코드

- 기계어를 사람이 이해할 수 있도록 의미를 부여한 명령

3) 어셈블리어 (니모닉 + α(지시, 매크로 등))

- 니모닉 코드 수준으로 직접 프로그래밍 할 수 있게 만든 언어

-

명령어

1) 명령어의 구성 (ex. ADD A, B, C)

○ OP 코드(Operation Code) (ADD)

- 동사 (~한다.)

○ 오퍼랜드(Operand) (A, B, C) (B+C 값을 A에 넣어라)

- 목적어 (~을)

2) 명령어 set에 따른 프로세서 종류

구분

CISC (Complex Instruction Set Computer)

RISC (Reduced Instruction Set Computer)

역사

1960 년대

1950 년대

특징1

메모리 참조 연산

Load / Store 구조

특징2

- 필요한 명령어를 그냥 때려넣듯 추가

- 중복되는 명령어가 많았다.

- 명령어의 크기 제각각

- 학문적으로 정리하여 다시 만듬.

- 중복명령어 제거.

- 명령어 크기 일정

명령어

복잡

단순

성능

낮다

높다

-

폰 노이만(Von-Neumann) 아키텍처

- 명령어와 데이터가 동일한 버스를 사용한다.

- 같은 버스를 사용하기 때문에 명령어를 읽을 때 데이터를 읽거나 쓸 수 없다.

- PC(개인용 PC), ARM7(v3)

-

하버드(Harvard) 아키텍처

- 명령어와 데이터가 개별 버스를 사용.

- 명령어를 읽을 때 데이터를 읽거나 쓸 수 있어 성능 향상.

- 버스 시스템이 복잡해지고 설계가 어려워 진다.

- ARM9(v4,5) ARM11(v6), Xscale(v5te) 등

-

Cache 메모리 시스템

1) 캐시(Cache) 존재 유무

- Cache 없을 시 : 고속의 CPU(400MHz)가 버스(66MHz) 및 메모리(10MHz)의 속도에 의존적이여서 늦다.

- Cache 있을 시 : CPU 주변에 고속의 메모리를 두고 자주 사용되는 명령과 데이터를 저장하여 시스템 성능을 개선.

2) 캐시(Cache)의 성능- Hit 의 비율이 높을 수록 성능이 좋아진다.(miss 비율 높으면 나빠짐)

- miss 발생시, Cache제어기는 시스템메모리 장치에서 Line 크기만큼 명령이나 데이터를 Cache로 읽어(Line Fill)들인다. (Line 단위 : 1000번지 읽으면 1004번지, 1008번지를 가져와 채워둠)

3) 캐시의 쓰기동작

- Write Back (copy back) : 캐시에만 쓰기 동작을 하고, 외부의 메모리에는 나중에 기록된다. (일반적인 경우)

- Write Through : 캐시와 외부 메모리에 모두 쓰기동작을 한다. (캐시 존재의 의미가 있나?)

-

MMU (Memory Management Unit)

1) 메모리 보호 기능

- 서로 보호되면서 실행된다. (ex. 포인터 잘못 접근을 보호해줌)

2) 어드레스 변환 기능

- CPU에서 사용되는 logical한 virtual 어드레스를 physical 어드레스로 변환해준다.

- 즉, 불 연속적인 메인 메모리의 물리적 주소를 CPU내에 연속적인 가상의 주소로 만든다. => 메모리 효율이 증가.

-

주변 장치 (I/O Device)

CPU가 입출력 기기에 접속하는 방법

구분

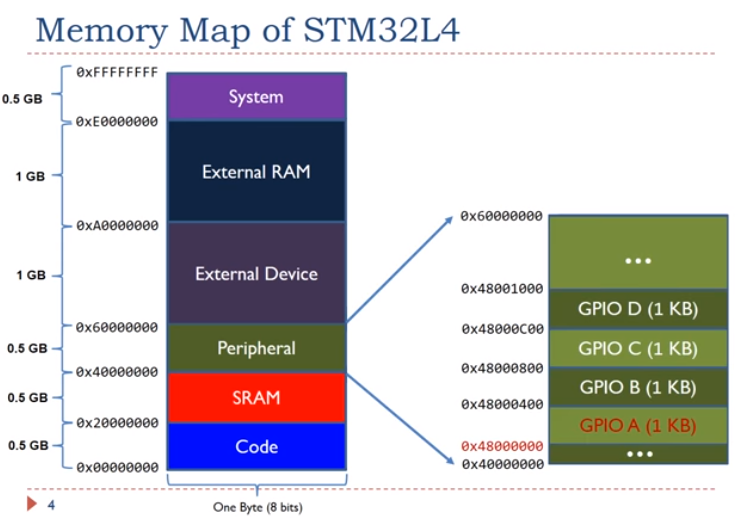

Memory Mapped I/O

I/O-mappd I/O

대표적인 CPU

ARM, PowerPC, M68K

x86계열

I/O 장치의 영역

메모리의 일부를 I/O 장치로 사용

메모리 영역과는 별도의 I/O 번지 영역이 존재

명령어

메모리와 I/O장치 모두 메모리 동작명령으로 엑세스

각 영역의 구분은 어드레스로 함.

메모리 엑세스 명령과 I/O 액세스명령(in/out)이 구분

하드웨어

어드레스를 해석하는 디코더 회로에 따라 메모리 or I/O장치가 선택

메모리 번지와 I/O 번지를 구분하는 신호가 존재

기타

- I/O 영역은 Non-cacheable로 설정

=> 실시간 실제 값 말고 캐시값을 읽을 경우가 생겨서

- I/O영역 변수는 volatile type 으로 선언

=> 컴파일러가 편집하지 말아야 실시간 값 저장가능.

-

자원 관리

1) Polling

- 장치가 프로세서에 의해 수동적으로 접근되어 지는 방식.

- 주로 loop문을 동며 각 장치를 순회하는 방식의 접근 방식.

2) Interrupt

- 장치가 프로세서를 불러 능동적으로 데이터나 에러를 처리하는 방식.

- 프로세서는 Polling에서처럼 주기적인 모니터링을 하지 않아도 된다.

3) DMA (Direct Memory Access)

- CPU의 개입없이 I/O장치와 기억장치 사이에 데이터를 전송하는 방식.

2. ARM Architecture

- ARM사는 직접 반도체를 제조하여 판매하는 것이 아니라 설계한 프로세서를 반도체 회사에 Hard Macrocell(레이아웃 수준 설계, 설계변경 불가능, 코어크기, 전압 고정) 또는 Synthesizable(HDL을 사용하여 RTL 수준 제공, 코어크기, 내부 메모리 변경가능, 기능 변경불가)로 제공

- ARM Architecture (위키백과)

- ARM core의 기본 구조를 일컫는 말. 처리되는 데이터의 사이즈, 명령어의 구조, 레지스터 등과 같은 추상적인 구성 및 동작원리 -

ARM Architecture 의 특징

1) 32bit RISC Architecture

- 명령어와 내부 레지스터가 32비트로 구성

- RISC(Reduced Instruction Set Computer)

2) 다양한 명령어 지원

- 32bit ARM 명령과 16비트 Thumb 명령을 제공

- 16bit Thumb 명령 : (Thumb 명령어가 탄생한 계기)

32 bit ARM 명령에 기초하여 16bit 길이로 opcode를 구성. 코드 크기를 줄이고, 8 또는 16비트 메모리 인터페이스에서 효과적으로 명령어 처리

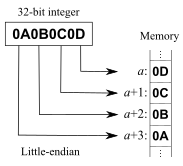

3) Big / Little Endian 지원

○ Endian 방식 : 메모리에 여러 바이트의 내용을 저장할 때 상위 바이트 및 하위 바이트의 위치를 결정하는 방식.

○ Big-Endian : 상위 바이트의 메모리를 하위 어드레스에 놓는 방식 (모토로라 계열 CPU)

○ Little Endian : 하위 바이트의 메모리를 하위 어드레스에 위치하는 방식 (Intel 계열 cpu)Big-Endian

Little-Endian

상위 바이트의 메모리를 하위 어드레스에 놓는 방식

하위 바이트의 메모리를 하위 어드레스에 놓는 방식

4) Fast Interrupt 지원

- ARM은 fast 인터럽트를 위한 별도의 레지스터를 가지고 있어 인터럽트 서비스 루틴(ISR)을 작성할 때 레지스터를 저장하고 복구하는 시간을 줄일 수 있다.

3. 프로그래머스 모델 (Programmer's Model)

- 프로그래머가 프로그램(어셈블리어)을 작성하는데 필요한 각종 정보. -> ARM의 Architecture를 구분하는 기준.

-

알아야 할 정보.

1) 명령어

2) 메모리 구조

3) 데이터 구조

4) 프로세서의 동작모드

5) 프로세서 내부 레지스터의 구성 및 사용법

6) Exception 처리

7) 인터럽트 처리

-

명령어(Instruction Set)

○ ARM 프로세서의 명령어

1) 32비트 ARM Instruction Set

- 모든 ARM 명령어는 조건부 실행이 가능하다.

- 모든 ARM 명령은 32bit로 구성. => 파이프라인 구성용이, 명령 디코더 구현 용이, 고속으로 처리 가능.

- Load / Store 같은 메모리 참조 명령이나 Branch 명령에서는 모두 상대주소(Indirect Address)(내 주소위치에서 + α) 방식을 사용.

- ARM 명령은 크기 11개의 기본적은 Type으로 구분.

-

16 비트 Thumb 명령어

- 32비트의 ARM 명령을 16 비트로 재구성한 명령

○ 장점

- 코드의 크기를 줄일 수 있다.

- 8비트나 16비트와 같은 좁은 메모리 인터페이스에서 ARM 명령을 수행 할 때 보다 성능이 효율적이다.

○ 단점

- 조건부 실행이 안된다.

- Immediate 상수 값이 표현 범위가 적다.

-

ARM / Thumb Interwork

- ARM state <-> Thumb state 로 상태가 전환되는 작업 => BX 명령에 의해 이루어진다.

-

ARM 프로세서 코어는 파이프라인을 지원

- 프로세서의 모든 부분들과 메모리 장치들이 계속적으로 쉬지 않고 동작한다.

- 하나의 명령이 수행되고 있는 동안에 다음에 수행할 명령을 decode하고, 그 다음에 수행할 명령이 메모리로부터 읽어 온다.

-

메모리 구조

- 메모리는 프로그램과 데이터를 저장하는 공간.

○ ARM에서 사용 가능한 데이터 타입

- 1byte

- Halfword : 2 바이트

- word : 4바이트

-

Operating Mode

-현재 프로세서가 어떤 권한을 가지고 어떤 종류의 작업을 하고 있는지를 나타낸다.

1) User 모드

- User task 또는 어플리케이션을 수행할 때의 프로세서의 동작 모드

- ARM 프로세서의 동작 모드 중 유일하게 Un-privileged 모드로 메모리나 I/O 장치와 같은 시스템 자원을 사용하는데 제한이 있다.

2) FIQ(Fast Interrupt Request) Mode

- 빠른 인터럽트의 처리를 위한 프로세서의 동작 모드

3) IRQ(Interrupt Request) Mode

- 일반적으로 사용되는 인터럽트를 처리하기 위한 프로세서의 동작모드

4) SVC(Supervisor) MODE (전원 키면 default)

- 시스템 자원을 관리할 수 있는 프로세서의 동작모드

- Operating 시스템의 커널이나 드라이버를 처리하는 모드

- Reset이나 소프트웨어 인터럽트(SWI)가 발생하는 ARM은 Supervisor 모드가 된다.

5) Abort Mode

- 명령이나 데이터를 메모리로부터 읽거나 쓸 때 오류가 발생하면 ARM은 Abort 모드가 된다.

- Abort는 외부의 메모리 제어기에서 발생.

6) Undefined Mode

- ARM이 정의되지 않은 명령을 수행하려고 하면 수행되는 프로세서의 동작모드.

7) System Mode (privilege user 모드)

- User 모드와 동일한 용도로 사용되지만 Privilege 모드이다.

- ARM Architecture v4이후부터 지원.

-

Operating Mode의 변경

1) Exception

- IRQ, FIQ를 비롯한 대부분의 Operating 모드는 외부에서 발생되는 조건에 의해 ARM 프로세서가 하드웨어적으로 변경한다.

- 외부에서 발생되는 물리적인 조건에 의해서 정상적인 프로그램의 실행을 미루고 예외적인 현상을 처리하는 것을 Exception이라 한다.

- Operating 모드의 변경은 소프트웨어에 의해 제어할 수도 있다.

2) 시스템 콜 (System Call)

- User 모드에서 수행되는 프로그램에서 Supervisor 모드로 전환하여 시스템 자원을 사용할 수 있게 해주는 인터페이스

- OS에서는 소프트웨어 인터럽트(SWI)를 사용하여 시스템콜을 구현

-

레지스터 (Register)

- 프로세서가 작업을 하는데 사용되는 값을 저장하는 공간.

- ARM에는 32bit 길이의 37개의 레지스터가 있다. (30개의 범용 + 1개의 PC + 1개의 CSPR + 5개의 SPSP = 37개)

1) 30개의 범용 레지스터

- 대부분 데이터 연산등에 사용

- 프로세서의 동작 모드에 따라 사용되는 레지스터가 제한된다.

2) 1개의 프로그램 카운터(PC)

- 프로그램을 읽어올 메모리의 위치를 나타낸다.

3) 1개의 CPSR

- 프로세서가 수행하고 있는 현재의 동작 상태를 나타낸다.

4) 5개의 SPSR

- 이전 모드의 CPSR의 복사본으로 Exception이 발생하면 ARM이 하드웨어적으로 이전 모드의 CPSR 값을 각각의 모드에 해당하는 SPSR에 복사

- User, System 모드를 제외한 모든 Privilege 모드에 각각 하나씩 존재.

-

Operating 모드 별로 사용 가능한 레지스터

○ ARM state의 경우

- 16개의 범용 레지스터 (R0~R15의 키워드를 사용하여 관리).

- R0~R12는 연산 명령과 같은 범용. R13(SP), R14(LR), R15(PC)는 특수한 목적으로 사용. (연산명령에서 사용할 수도 있다.)

- 1개의 CPSR, privilege 모드의 경우 각각 1개의 SPSR(총 5개)

○ Thumb state의 경우

- 8개의 범용 레지스터 (R0~R7)

- R13(SP), R14(LR), R15(PC) 레지스터 (연산 명령에서 사용 불가)

- 1개의 CPSR, privilege 모드의 경우 각각 1개의 SPSR

- Operating 모드 별 레지스터

○ Stack Pointer (SP 또는 R13) : 프로그램에서 사용하는 스택의 위치를 저장하는 레지스터

- 프로세서의 동작 모드마다 별도로 할당된 SP레지스터를 가지고 있다.

- ARM은 별도의 스택 명령이 없다. (Push, Pop 과 같은 별도의 스택 명령을 제공하지 않는다.)

=> LDR / STR, LDM / STM 같은 데이터 전송 명령을 사용하여 스택을 처리

○ Link Register (LP 또는 R14) : 서브루틴에서 되돌아 갈 위치 정보를 저장하고 있는 레지스터

- 서브루틴을 호출하는 BL(Branch with Link)명령을 사용하면 PC값을 자동으로 LR에 저장(함수 종료 후 되돌아갈 주소 저장)

- 되돌아 갈 때는 MOV 명령을 이용하여 LR 값을 PC에 저장. (MOV PC, LR)

- ADD나 SUB와 같은 연산 명령을 이용하여 되돌아갈 위치를 조정할 수도 있다.

- 프로세서의 동작 모드마다 별도로 할당된 LR 레지스터를 가지고 있다.

○ Program Counter (PC또는 R15) : Fetch할 주소를 저장하고 있는 레지스터

- ARM state의 경우 위치정보 비트 [31:2] 저장 -> 4byte(32bit) 단위의 주소

- Thumb state의 경우 위치정보 비트 [31:1] 저장 -> 2byte(16bit) 단위의 주소

- 다른 범용 레지스터와 마찬가지로 ADD, SUB와 같은 연산명령을 사용하여 프로그램이 분기할 위치 조정 가능

- 프로세서의 모든 동작 모드에 대하여 하나만 존재한다.

* 개인적인 학습 목적으로 작성한 글이기에 내용에 잘못된 정보가 있을 수 있습니다.

'임베디드 개발(before) > IoT 임베디드 SW 개발자 양성과정' 카테고리의 다른 글

| [28일차] ARM 프로세서 이해 및 활용(ARM 프로세서의 명령어) (0) | 2020.08.20 |

|---|---|

| [27일차] ARM 프로세서 이해 및 활용 (Program Status Register (PSR), Exception) (0) | 2020.08.19 |

| [25일차] 탐색 알고리즘(순차, 이분, 이진트리, 레드-블랙, 해쉬) (0) | 2020.08.14 |

| [24일차] 정렬 알고리즘(선택, 삽입, 거품, 쉘, 퀵, 기수, 힙) (1) | 2020.08.13 |

| [23일차] 스택(Stack) & 큐(Queue) & 트리(Tree) & 재귀함수(Recursive func) (1) | 2020.08.12 |